Platinum FET Test Chips, Optimized for 2D Materials

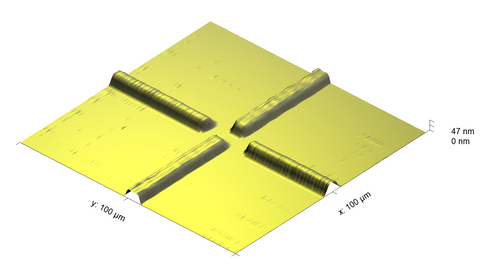

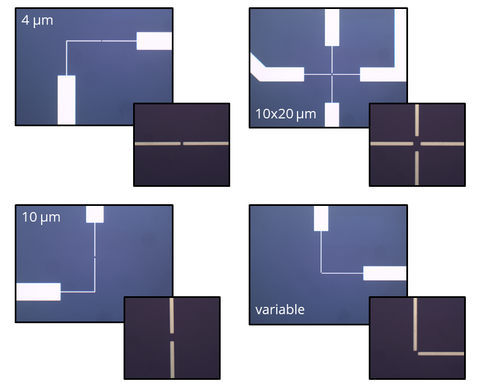

Ossila’s 2D material FET test chip is designed to allow users to perform electrical and optical measurements on monolayer or few-layer 2-dimensional (2D) crystals, without the need for expensive lithography equipment. Our chips come prepatterned with platinum electrodes on a Si-SiO2 substrate, with source-drain channel lengths ranging from 4 µm to 20 µm. Transfer your crystal across the channel and you are ready to measure. The chips also feature dual channel electrodes that allow you to stack two crystals on top of each other and contact each separately.

Research into 2D materials has been steadily growing in popularity for several years, fuelled by the promise of revolutionary new technology in areas ranging from batteries to quantum computers. The preferred method for 2D material preparation (within the research community at least) is the so-called 'Scotch-tape' method, where monolayer or few-layer crystals are peeled from bulk material. This method currently gives the highest quality 2D materials needed for optical and electronic applications. The preparation of 2D materials in this way is relatively straightforward, and optical measurements can require little more than a microscope and a light source.

However, to reach their full potential, the electrical characteristics of 2D materials needs to be studied. This posses a large barrier to entry for the researcher, as complicated and expensive lithography equipment is required to create the electrical contacts to the 2D crystals. We have developed our 2D material FET substrates in partnership with researchers in the field to remove this barrier, and to speed up the electrical and optical characterisation of 2D materials.

| Substrate / Gate | Silicon (n-doped) |

| Gate resistivity | ~5 Ωcm |

| Gate dielectric | 300 nm thermally grown silicon dioxide |

| Dimensions | 14.97 mm x 14.97 mm x 0.7 mm |

| Electrode pad pitch | 1.27 mm |

| Electrode width | 4 µm |

| Electrode material | Platinum (50 nm ± 10 nm) / Titanium adhesion layer (5 nm) |

| Deposition method | Plasma sputtering |

| Patterning method | Photolithography |

| Channel lengths |

4 µm (2x) 10 µm (2x) 4 µm x 10 µm 4 µm x 20 µm 10 µm x 20 µm 10 µm x 20 µm variable length (x4) |

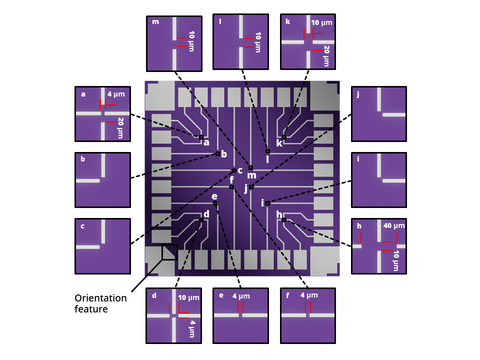

Electrode layout

The platinum is sputtered onto a titanium adhesion layer to provide an extremely robust contact and channel allowing it to withstand cleaning procedures such as solvent sonication, plasma etching, and swabbing.

Electrical measurements on small 2D crystals can be tricky. It usually involves a multistage process consisting of:

- Exfoliation of a bulk crystal into a 2d flakes

- Locating a suitable flake

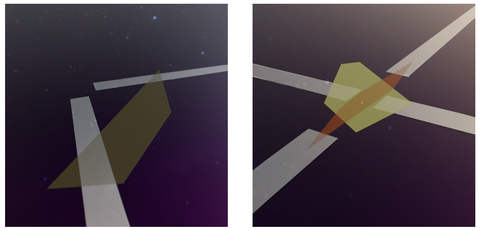

- Transfer of the flake onto a substrate

- Designing electrodes around the flake

- Patterning of electrodes, usually using ebeam lithography

- Metal deposition and lift-off

The Ossila test chips optimized for 2D materials help simplify this workflow by providing pre-patterned platinum electrodes onto which a flake can be directly transferred. This eliminates the need for access to lithography and deposition systems.

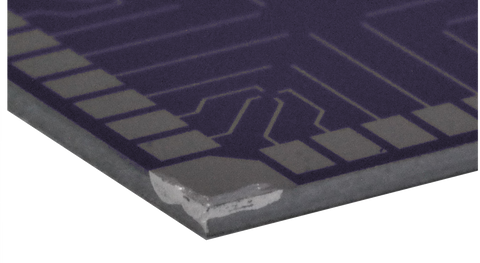

The electrode contacts are placed along the edges of the test chip, allowing optical measurements to be carried out without obstruction from wires.

Cleaning

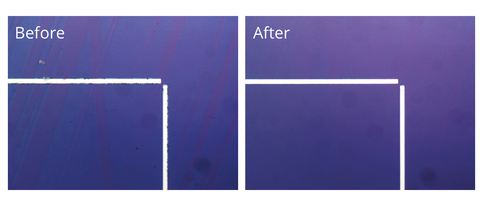

Your substrates may arrive with a residue from the photolithography process used to create the electrodes. We recommend cleaning the substrates before use by sonication in warm isopropanol for 10 minutes, followed by drying with compressed nitrogen. The substrates may be cleaned and reused as needed.

Sample preparation

Our guide to 2D exfoliation will walk you through the process preparing a suitable crystal for transfer, and deterministically positioning a flake on a substrate.

Electrical connections

The 32 rectangular pads are source-drain contacts. Once a flake has been positioned across the channel, the pads connected to electrodes on each side of the channel should be identified and a voltage applied across them. There are 3 different electrode geometries on the chip:

- Dual electrodes in an inline configuration with fixed channel width (4 µm and 10 µm)

- Quad electrodes in cross configuration with fixed channel widths (4 µm x 10 µm, 4 µm x 20 µm, 10 µm x 20 µm and 10 µm x 40 µm)

- Dual electrodes in a perpendicular configuration which allows the channel width to be defined by the size of the crystal

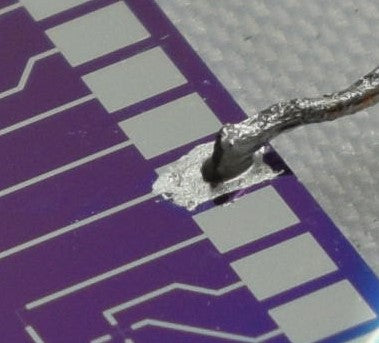

A probe station can be used to connect to the pads. Alternatively, a wire can be attached using conductive silver paint.

The gate can be contacted directly through the substrate bottom or edges, or the 4 corner pads can act as the gate contact. If using the corner pads, we recommend applying silver (conductive) paint along and around the pad edges to make a connection with the substrate edge.

Over time a native oxide layer of a few nanometers thickness will build up on the exposed silicon. Removing this will allow a lower resistance electrical connection to the gate. If required, we recommend removing the native oxide mechanically by using a fine grit sandpaper or scratching the silicon area before making the contact. We do not recommend chemical removal of the native oxide as this process may damage the platinum electrodes and gate dielectric.